ImperasDV 是一种基于 RISC-V 指令集架构 (ISA) 的定制处理器前端设计验证解决方案。它包括参考模型、验证组件、功能覆盖、测试套件和调试器。

由于RISC-V是一个开放标准的指令集,它允许任何开发人员自由地设计和扩展自定义处理器,同时与日益增长的支持工具和软件的生态系统保持兼容。RISC-V处理器验证需要一种与指令集的可配置和可扩展特性相匹配的解决方案。它必须能够与用户的现有环境配合使用,并且应利用诸如RISC-V验证接口(RVVI)这样的开放标准接口,以实现效率和代码重用。RISC-V验证解决方案应支持诸如约束随机刺激和功能覆盖等行业最佳实践。解决方案必须解决处理器特定的挑战,即验证DUT在响应异步事件时的行为,因为这些事件是常见错误的来源。

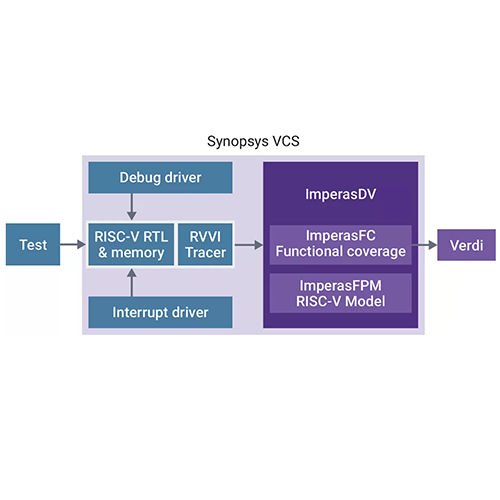

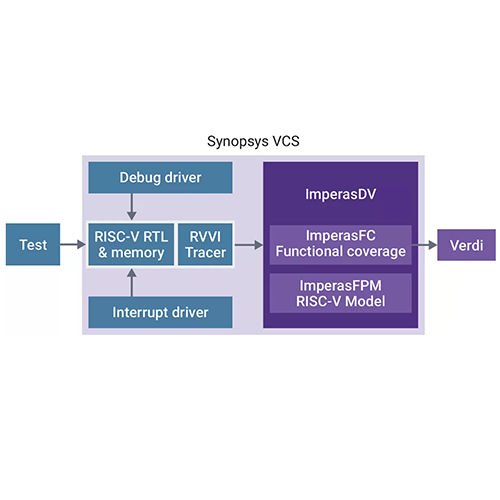

ImperasDV 是一个满足所有这些要求的解决方案。它使用 ImperasFPM(快速处理器模型)作为设计验证的参考模型。该模型可以配置和扩展以匹配被测处理器,包括自定义功能。ImperasDV 可以用于 SystemVerilog/UVM 测试平台,或与任何具有 C 接口的语言一起使用。它使用 RVVI-TRACE 接口连接到被测处理器,并提供连续的架构状态比较和检查。它使用一种新颖的流水线同步技术来处理异步事件的随机发生。ImperasDV 还为 RISC-V ISA 中的每个扩展提供一个机器生成的功能覆盖模型。

关键优势

基于参考模型的解决方案

使用经过行业验证的Imperas RISC-V快速处理器模型

盒外解决方案

启动您的CPU验证。实例化并连接ImperasDV

立即报告错误

缩短调试时间,避免模拟周期的浪费

查找复杂错误

涉及随机刺激和异步事件

ImperasDV如何工作?

在RTL和ImperasFPM上并行执行相同的程序。ImperasDV使用锁步连续比较,这是一种cosimulation方法,其中RTL和参考模型以锁步方式运行。当每条指令执行完毕时,比较两个的架构状态。架构状态的不匹配将立即作为错误报告。

通过这种全面的设计验证方法,可以立即报告错误,不需要运行模拟循环直到第一个错误,而且更容易在失败点进行调试。传统的模拟后跟踪文件和签名比较方法可能会错过错误,导致时间浪费。

ImperasDV 与 Synopsys VCS 合作进行 RISC-V RTL 模拟。功能覆盖输出发送到 Verdi®,这是一个调试和验证管理平台,包括 AI 技术以自动化复杂的调试步骤。使用 ImperasDV 和 Synopsys VCS 可以降低 RTL 风险并加速验证计划。ImperasTS 为 RISC-V ISA 提供了用于复杂和可配置扩展集的测试套件。ImperasDV 还可以与 Synopsys 领先的硬件辅助验证 (HAV) 解决方案 HAPS 和 ZeBu 一起使用,用于 RISC-V 处理器的仿真和原型设计。

特性

如果您对此感兴趣,欢迎问问展商吧!

如果您对此感兴趣,欢迎问问展商吧!

暂无数据

暂无数据 暂无数据

暂无数据 如果您对此感兴趣,欢迎问问展商吧!

如果您对此感兴趣,欢迎问问展商吧!